# DIAMOND SYSTEMS CORPORATION

# **DIAMOND-MM-AT**

Autocalibrating 12-bit Analog I/O PC/104 Module

User Manual V1.21

© Copyright 2004

Diamond Systems Corporation

8430-D Central Ave.

Newark, CA 94560

Tel (510) 456-7800

Fax (510) 456-7878

techinfo@diamondsystems.com

www.diamondsystems.com

# **TABLE OF CONTENTS**

| 1.  | DESCRIPTION                             | 3  |

|-----|-----------------------------------------|----|

| 2.  | I/O HEADER PINOUT AND PIN DESCRIPTION   | 4  |

| 3.  | BOARD CONFIGURATION                     | 5  |

| 4.  | DIAMOND-MM-AT BOARD DRAWING             | 8  |

| 5.  | I/O MAP                                 | 9  |

| 6.  | REGISTER DEFINITIONS                    | 11 |

| 7.  | ANALOG INPUT RANGES AND RESOLUTION      | 21 |

| 8.  | ANALOG INPUT RANGE SETTINGS             | 22 |

| 9.  | PERFORMING AN A/D CONVERSION            | 23 |

| 10. | A/D SCAN, INTERRUPT, AND FIFO OPERATION | 26 |

| 11. | ANALOG OUTPUT RANGES AND RESOLUTION     | 28 |

| 12. | GENERATING AN ANALOG OUTPUT             | 29 |

| 13. | DIGITAL I/O OPERATION                   | 30 |

| 14. | SPECIFICATIONS                          | 31 |

| 15. | 82C54 COUNTER/TIMER DATASHEET           | 32 |

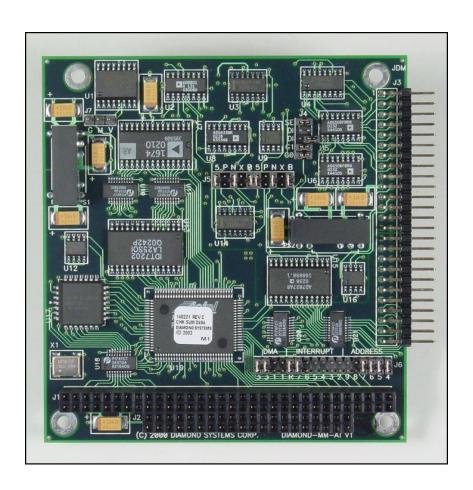

# 1. DESCRIPTION

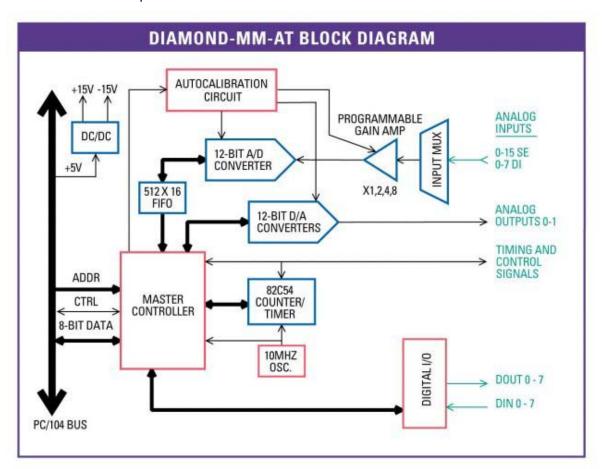

Diamond-MM-AT (DMM-AT) is a full-featured 12-bit analog I/O PC/104 module containing both analog input and analog output channels along with digital I/O and counter/timers. The register map and connector pinout of this board are the same as on our Diamond-MM (DMM) board, enabling DMM-AT to be a drop-in replacement for most existing DMM applications. DMA is not supported on this board.

#### **Features**

- 16 analog inputs

- 12-bit A/D converter, 100KHz maximum sampling rate

- Programmable gain

- A/D FIFO for reduced interrupt overhead

- 2 12-bit D/A channels

- · 8 digital inputs

- 8 digital outputs

- 32-bit counter/timer for A/D timing

- 16-bit counter/timer for user application

- Programmable clock sources for counter/timers

- Autocalibration of analog input and output circuitry

- Programmable D/A full-scale range

- -40 to +85°C operation standard

# 2. I/O HEADER PINOUT AND PIN DESCRIPTION

Diamond-MM-AT provides a 50-pin header labeled J3 for all user I/O.

| Vin 15 / 7- | 1  | 2  | Vin 7 / 7+       |

|-------------|----|----|------------------|

| Vin 14 / 6- | 3  | 4  | Vin 6 / 6+       |

| Vin 13 / 5- | 5  | 6  | Vin 5 / 5+       |

| Vin 12 / 4- | 7  | 8  | Vin 4 / 4+       |

| Vin 11 / 3- | 9  | 10 | Vin 3 / 3+       |

| Vin 10 / 2- | 11 | 12 | Vin 2 / 2+       |

| Vin 9 / 1-  | 13 | 14 | Vin 1 / 1+       |

| Vin 8 / 0-  | 15 | 16 | Vin 0 / 0+       |

| Agnd        | 17 | 18 | Vref Out         |

| Agnd        | 19 | 20 | Vout 0           |

| Agnd        | 21 | 22 | Vout 1           |

| Agnd        | 23 | 24 | +15V             |

| -15V        | 25 | 26 | Vref In 0        |

| Agnd        | 27 | 28 | Vref In 1        |

| In 0-       | 29 | 30 | Dgnd             |

| Out 0       | 31 | 32 | Out 2            |

| Dout 7      | 33 | 34 | Dout 6           |

| Dout 5      | 35 | 36 | Dout 4           |

| Dout 3      | 37 | 38 | Dout 2           |

| Dout 1      | 39 | 40 | Dout 0           |

| Din 7       | 41 | 42 | Din 6            |

| Din 5       | 43 | 44 | Din 4            |

| Din 3       | 45 | 46 | Din 2 / Gate 0   |

| Din 1       | 47 | 48 | Din 0 / Gate 1/2 |

| +5V         | 49 | 50 | Dgnd             |

|             |    |    |                  |

| Signal Name          | Definition                                                                                                                          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Vin 7/7+ ~ Vin 0/0+  | Analog input channels 7 - 0 in single-ended mode;<br>High side of input channels 7 - 0 in differential mode                         |

| Vin 15/7- ~ Vin 8/0- | Analog input channels 15 - 8 in both single-ended mode;<br>Low side of input channels 7 - 0 in differential mode                    |

| Vout0, Vout 1        | Analog output channels 0 and 1                                                                                                      |

| Vref Out             | +5V or -5V precision reference voltage output (user selectable)                                                                     |

| Vref In 0, 1         | External reference voltage inputs for custom D/A full-scale ranges                                                                  |

| Dout7 - Dout0        | Digital output port, TTL / CMOS compatible                                                                                          |

| Din7 - Din0          | Digital input port, TTL / CMOS compatible                                                                                           |

| Din2 / Gate 0        | Digital input line 2 doubles as the gate control for counter 0;<br>Counter 0 counts when this line is high and holds when it is low |

| Din0 / Gate 1/2      | Digital input line 0 doubles as a gate signal for counters 1 and 2 as determined by the control register at base + 11               |

| In0-                 | Counter 0 input, negative polarity (negative edge trigger)                                                                          |

| Out0, Out2           | Counter 0 and Counter 2 output signals                                                                                              |

| ±15V                 | Analog power supply; maximum current draw 10mA per line                                                                             |

| +5V                  | Connected to PC/104 bus power supply CAUTION: Power supply outputs are not short-circuit protected!                                 |

| Agnd                 | Analog ground                                                                                                                       |

# 3. BOARD CONFIGURATION

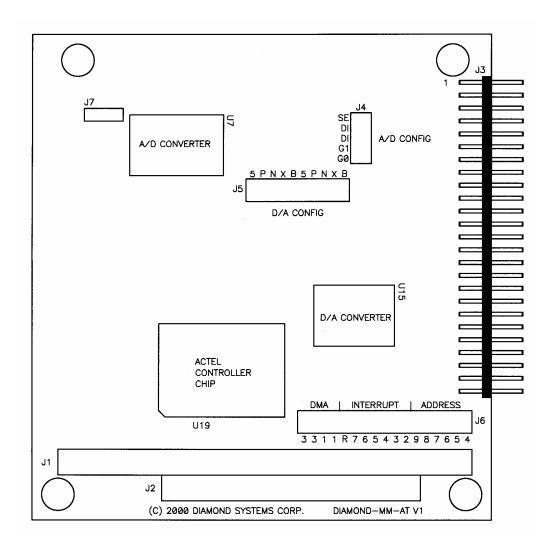

Refer to the Drawing of Diamond-MM-AT in chapter 4 for locations of the configuration items mentioned here.

#### 3.1 Base Address

Each board in the system must have a different base address. Diamond-MM-AT's base address is set with J6, located at the lower right corner of the board. Each of the six jumper locations marked 9, 8, 7, 6, 5, 4 corresponds to the same-numbered address bit. A jumper out is equal to a 1, and a jumper in is equal to a 0. The jumpers correspond to address bits 9-4 and leave bits 3-0 unselected, resulting in a 16-byte I/O decode. Although any 16-byte location is selectable, certain locations are reserved or may cause conflicts with other system resources. The table below lists recommended base address settings for Diamond-MM-AT. The default setting is 300 Hex.

| Base . | Address       |     | J   | umper F | Position |     |     |

|--------|---------------|-----|-----|---------|----------|-----|-----|

| Hex    | Decimal       | 9   | 8   | 7       | 6        | 5   | 4   |

| 220    | 544           | Out | In  | In      | In       | Out | In  |

| 240    | 576           | Out | In  | In      | Out      | In  | In  |

| 250    | 592           | Out | In  | In      | Out      | In  | Out |

| 260    | 608           | Out | In  | In      | Out      | Out | In  |

| 280    | 640           | Out | In  | Out     | In       | In  | In  |

| 290    | 656           | Out | In  | Out     | In       | In  | Out |

| 2A0    | 672           | Out | In  | Out     | In       | Out | In  |

| 2B0    | 688           | Out | In  | Out     | In       | Out | Out |

| 2C0    | 704           | Out | In  | Out     | Out      | In  | In  |

| 2D0    | 720           | Out | In  | Out     | Out      | In  | Out |

| 2E0    | 736           | Out | In  | Out     | Out      | Out | In  |

| 300    | 768 (Default) | Out | Out | In      | In       | In  | In  |

| 330    | 816           | Out | Out | In      | In       | Out | Out |

| 340    | 832           | Out | Out | In      | Out      | In  | In  |

| 350    | 848           | Out | Out | In      | Out      | In  | Out |

| 360    | 864           | Out | Out | In      | Out      | Out | In  |

| 380    | 896           | Out | Out | Out     | In       | In  | In  |

| 390    | 912           | Out | Out | Out     | In       | In  | Out |

| 3A0    | 928           | Out | Out | Out     | In       | Out | In  |

| 3C0    | 960           | Out | Out | Out     | Out      | In  | In  |

| 3E0    | 992           | Out | Out | Out     | Out      | Out | In  |

#### 3.2 J4: A/D Single-Ended / Differential Mode and Programmable Gain

A/D input channels may be either single-ended (two wires consisting of input and ground) or differential (three wires consisting of input+, input-, and ground). All inputs on DMM-AT must be configured in the same manner. To select single-ended inputs, install one jumper in the SE position on J4. To select differential inputs, install two jumpers **horizontally** in the two DI positions. If you install these two jumpers vertically the inputs will not function properly.

Analog inputs may also be configured for unipolar (positive voltages only) or bipolar (both positive and negative voltages) operation. This configuration is done in software.

In most applications programmable gain is desirable. It enables you to select the gain for each input channel independently in software. To select programmable gain, install two jumpers **horizontally** in the G1 and G0 positions on J4. This connects the gain control pins on the Actel controller chip to the gain amplifier inputs so that software can control the gain setting.

For backward compatibility with Diamond-MM, the input gain may be set with jumpers. To do this, install jumpers in G1 and/or G0 to select the gain according to the table below. Also make sure that your program does not modify the two control bits G1 and G0 in the register at Base + 11. The Diamond-MM driver software does not use this register, so if you install a Diamond-MM-AT board in a system using software written for the Diamond-MM, the gain setting will remain constant according to your selection.

# **Jumper Settings for Fixed Gain Only**

| Gain | G1  | G0  |

|------|-----|-----|

| 1    | In  | In  |

| 2    | In  | Out |

| 4    | Out | In  |

| 8    | Out | Out |

## 3.3 J5: D/A Configuration

The two analog outputs may be configured for unipolar/bipolar operation, and their full-scale may be either a fixed value from an on-board fixed reference, a programmable value from an on-board programmable reference, or a user-provided value from a pin on the I/O header. Each output channel may be configured independently. Jumper block J5 is used for the analog output configuration. Channel 0 uses the left group of 5 pairs, and channel 1 uses the right group of 5 pairs. Each group is labeled 5 P N X B.

The three items to configure are: internal/external reference; if internal, fixed or programmable; and finally unipolar/bipolar operation:

| Position | Function                                                              |

|----------|-----------------------------------------------------------------------|

| 5        | Selects 5V reference (if N jumper is installed)                       |

| Р        | Selects programmable reference (if N jumper is installed)             |

| N        | Selects internal reference, 5 or P above                              |

| X        | Selects external reference, J3 pin 26 for DAC 0 or J3 pin 28 for DAC1 |

| В        | Selects bipolar mode if in, unipolar mode if out                      |

For each DAC, one jumper must be installed in either N or X but not both.

For each DAC, if a jumper is installed in N, then one jumper must be installed in either 5 or P but not both.

If both DACs are set to P and N (internal programmable reference), then both DACs must have the same B jumper setting (in for both or out for both).

# 3.4 J6: Interrupt level and DMA level

To select the interrupt level, install a jumper in the location 7, 6, 5, 4, 3, or 2 in the interrupt portion of J6. Only one jumper should be installed in these locations. These are the only interrupt levels supported by Diamond-MM-AT.

In most instances you should also install a jumper in the R position to connect a  $1K\Omega$  pull-down resistor to the interrupt line. This enables interrupt sharing with other boards on the same interrupt level. Only one pull-down resistor should only be installed on any interrupt level on the PC/104 bus, so if you have two or more boards sharing the same interrupt level, be sure that only one of them has the R jumper installed.

DMA is not currently supported on the Diamond-MM-AT board due to the fact that the FIFO combined with interrupt operation enable the board to operate at full speed in any operating system supported by the DSC Universal Driver. However the configuration locations are provided for future upgrade. If DMA is required please contact technical support.

#### 3.5 J7: Test connector

J7 is used at the factory for initial board calibration and test. It is not needed by the user except in rare instances such as if the stored calibration values have accidentally been overwritten, or if you want to verify that the analog input circuit is functioning properly.

The 3 positions are marked G, M, and V. G is analog ground, M is the input signal from the output of the analog multiplexors (the currently selected input channel), and V is the output of the programmable gain amplifier (the voltage at M times the selected gain). Any gain and offset errors between M and V are corrected by the autocalibration circuit between this point and the A/D converter.

# 4. DIAMOND-MM-AT BOARD DRAWING

# 5. I/O MAP

# 5.1 Overview

Diamond-MM-AT occupies 16 bytes in I/O space. A functional list of registers is provided below, and detailed bit definitions are provided on the next page and the following chapter.

| Base + | Write Function                      | Read Function                      |

|--------|-------------------------------------|------------------------------------|

| 0      | Start A/D conversion                | A/D LSB + channel tag              |

| 1      | Reset FIFO                          | A/D MSB                            |

| 2      | A/D channel register                | A/D channel register               |

| 3      | Digital output port                 | Digital input port                 |

| 4      | D/A 0 LSB                           | Not used                           |

| 5      | D/A 0 MSB + update                  | Not used                           |

| 6      | D/A 1 LSB                           | Not used                           |

| 7      | D/A 1 MSB + update                  | Not used                           |

| 8      | Clear interrupt flip flop           | Status register                    |

| 9      | A/D operation control register      | A/D operation register readback    |

| 10     | Ctr/Timer and FIFO Control Register | Ctr/Timer / FIFO register readback |

| 11     | Analog Configuration Register       | Analog and FIFO register readback  |

Addresses 12-15 form a window into 2 4-byte pages.

| <u> Page 0: 8</u>                 | 2C54 counter/timer                                                                                                     |                                                                                                                |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 12                                | Counter/timer 0 data register                                                                                          | Counter/timer 0 data register                                                                                  |

| 13                                | Counter/timer 1 data register                                                                                          | Counter/timer 1 data register                                                                                  |

| 14                                | Counter/timer 2 data register                                                                                          | Counter/timer 2 data register                                                                                  |

| 15                                | Counter/timer control register                                                                                         | Counter/timer control register                                                                                 |

| Page 1: C<br>12<br>13<br>14<br>15 | Calibration  EEPROM / TrimDAC data register  EEPROM / TrimDAC address register  Calibration control register  Not used | EEPROM / TrimDAC data register<br>EEPROM / TrimDAC address register<br>Calibration status register<br>Not used |

# 5.2 Register Map Bit Assignments

# WRITE operations (blank bits are unused and have no effect)

|    | 7                       | 6                    | 5          | 4              | 3            | 2             | 1           | 0           |  |

|----|-------------------------|----------------------|------------|----------------|--------------|---------------|-------------|-------------|--|

| 0  |                         | Start A/D Conversion |            |                |              |               |             |             |  |

| 1  |                         |                      |            | Rese           | FIFO         |               |             |             |  |

| 2  | HIGH3                   | HIGH2                | HIGH1      | HIGH0          | LOW3         | LOW2          | LOW1        | LOW0        |  |

| 3  | DOUT7                   | DOUT6                | DOUT5      | DOUT4          | DOUT3        | DOUT2         | DOUT1       | DOUT0       |  |

| 4  | DA0-7                   | DA0-6                | DA0-5      | DA0-4          | DA0-3        | DA0-2         | DA0-1       | DA0-0       |  |

| 5  | SUD                     |                      |            |                | DA0-11       | DA0-10        | DA0-9       | DA0-8       |  |

| 6  | DA1-7                   | DA1-6                | DA1-5      | DA1-4          | DA1-3        | DA1-2         | DA1-1       | DA1-0       |  |

| 7  |                         |                      |            |                | DA1-11       | DA1-10        | DA1-9       | DA1-8       |  |

| 8  |                         |                      | Clea       | ar Interrupt F | Request Flip | Flop          |             |             |  |

| 9  | AINTE                   |                      |            |                | TINTE        | DMAEN         | CLKEN       | CLKSEL      |  |

| 10 | PAGE                    |                      | FIFOEN     | SCANEN         | CLKFRQ       | C2            | C1          | C0          |  |

| 11 |                         |                      |            |                | RANGE        | ADBU          | G1          | G0          |  |

| 12 |                         | Page 0: 8            | 2C54 Coun  | ter 0          | Page         | e 1: Calibrat | ion Data    |             |  |

| 13 | Page 0: 82C54 Counter 1 |                      |            |                | Page         | e 1: Calibrat | ion Address | 3           |  |

| 14 |                         | Page 0: 8            | 2C54 Coun  | ter 2          | Page         | e 1: Calibrat | ion Control |             |  |

| 15 |                         | Page 0: 8            | 2C54 Contr | ol Register    | Page         | 1: EEPRO      | M access k  | ey register |  |

# **READ operations** (blank bits are unused and read back as 0)

|    | 7                       | 6         | 5          | 4            | 3      | 2             | 1            | 0      |

|----|-------------------------|-----------|------------|--------------|--------|---------------|--------------|--------|

| 0  | AD3                     | AD2       | AD1        | AD0          | ADCH3  | ADCH2         | ADCH1        | ADCH0  |

| 1  | AD11                    | AD10      | AD9        | AD8          | AD7    | AD6           | AD5          | AD4    |

| 2  | HIGH3                   | HIGH2     | HIGH1      | HIGH0        | LOW3   | LOW2          | LOW1         | LOW0   |

| 3  | DIN7                    | DIN6      | DIN5       | DIN4         | DIN3   | DIN2          | DIN1         | DIN0   |

| 4  |                         |           |            | Not          | Used   |               |              |        |

| 5  |                         |           |            | Not          | Used   |               |              |        |

| 6  |                         |           |            | Not          | Used   |               |              |        |

| 7  |                         |           |            | Not          | Used   |               |              |        |

| 8  | STS                     | TINT      | SD         | AINT         | CH3    | CH2           | CH1          | CH0    |

| 9  | AINTE                   |           |            |              | TINTE  | DMAEN         | CLKEN        | CLKSEL |

| 10 | PAGE                    |           | FIFOEN     | SCANEN       | CLKFRQ | C2            | C1           | C0     |

| 11 | WAIT                    | OVF       | HF         | EF           | RANGE  | ADBU          | G1           | G0     |

| 12 |                         | Page 0: 8 | 32C54 Cour | nter 0       | Pag    | e 1: Calibrat | tion Data    |        |

| 13 | Page 0: 82C54 Counter 1 |           |            |              |        | e 1: Calibrat | tion Address | 3      |

| 14 |                         | Page 0: 8 | 32C54 Cour | nter 2       | Pag    | e 1: Calibrat | tion Status  |        |

| 15 |                         | Page 0: 8 | 32C54 Cont | rol Register | Pag    | e 1: FPGA r   | evision cod  | e      |

#### 6. REGISTER DEFINITIONS

In the register maps below, any blank bit location is unused. Writing to it has no effect, and reading it returns a 0.

# Base + 0 Read A/D LSB + Channel Tag

Bit No. 7 6 5 4 3 2 1 0 Name AD3 AD2 AD1 AD0 CH<sub>3</sub> CH2 CH<sub>1</sub> CH<sub>0</sub>

#### **Definitions:**

AD3 - 0 A/D data bits 3 - 0; AD0 is the LSB; A/D data is an unsigned 12-bit value.

CH3 - 0 A/D channel data, 0 - 15 (0 - 7 in differential mode)

#### Base + 0 Write Start A/D Conversion

Writing to Base + 0 starts an A/D conversion. The value written does not matter.

| Base + 1 | Read | A/D MSB   |

|----------|------|-----------|

| Dase T I | Reau | A/U IVIOD |

| Bit No. | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------|------|-----|-----|-----|-----|-----|-----|

| Name    | AD11 | AD10 | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 |

# **Definitions:**

AD11 - 4 A/D data bits 11 - 4; AD11 is the MSB; A/D data is an unsigned 12-bit value.

# Note: Reading from Base + 0 and Base + 1 result in the same physical operation, reading from the FIFO.

The FIFO is 8 bits wide, with A/D data stored and retrieved in interleaved fashion. Data from the A/D is put into the FIFO in little-endian mode, with the LSB and channel tag inserted first, and the MSB inserted second. Thus the data comes out of the FIFO in the same order. Each time a byte is read from either Base + 0 or Base + 1, the next byte will be read from the FIFO and the FIFO counter will be decremented.

Because the FIFO decrements after each read operation, you cannot read the same value more than once (unless the FIFO is empty, in which case the last byte may be read indefinitely). It is the programmer's responsibility to ensure that data is read out of the FIFO properly so that data underrun does not occur from extra read operations.

#### Base + 1 Write Reset FIFO

Writing to Base + 1 resets the FIFO. The value written does not matter. After writing to this address, EF = 1, HF = 0, and OVF = 0.

# Base + 2 Read/Write A/D Channel Register

| Bit No. | 7     | 6     | 5     | 4     | 3    | 2    | 1    | 0    |

|---------|-------|-------|-------|-------|------|------|------|------|

| Name    | HIGH3 | HIGH2 | HIGH1 | HIGH0 | LOW3 | LOW2 | LOW1 | LOW0 |

## **Definitions:**

HIGH3 - 0 High channel of channel scan range

Ranges from 0 to 15 in single-ended mode, 0 - 7 in differential mode.

LOW3 - 0 Low channel of channel scan range

Ranges from 0 to 15 in single-ended mode, 0 - 7 in differential mode.

The high channel must be greater than or equal to the low channel.

When this register is written, the current A/D channel is set to the low channel. The WAIT bit (base  $\pm$  11 bit 7) goes high for 10µS to indicate that the analog circuit is settling on the new input value. Do not start a new A/D conversion until WAIT returns to 0.

# Base + 3 Read Digital Input Port

| Bit No. | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Name    | DIN7 | DIN6 | DIN5 | DIN4 | DIN3 | DIN2 | DIN1 | DIN0 |

These signals correspond directly to the same-named pins on I/O connector J3.

All lines are connected to  $10K\Omega$  pull-up resistors.

| Base + 3 | Write | Digi  | ital Outpu | t Port |       |       |       |       |

|----------|-------|-------|------------|--------|-------|-------|-------|-------|

| Bit No.  | 7     | 6     | 5          | 4      | 3     | 2     | 1     | 0     |

| Name     | DOUT7 | DOUT6 | DOUT5      | DOUT4  | DOUT3 | DOUT2 | DOUT1 | DOUT0 |

These pins correspond directly to the same-named pins on I/O connector J3.

On power-up or reset, the output register is cleared to all zeroes.

| Base + 4 Write DAC 0 L |

|------------------------|

|------------------------|

| Bit No. | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name    | DA7 | DA6 | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 |

## **Definitions:**

DA7 - 0 D/A data bits 7 - 0 for output channel 0; DA0 is the LSB; D/A data is an unsigned 12-bit value.

| Base + 5 | Write | DAG | C 0 MSB |   |      |      |     |     |

|----------|-------|-----|---------|---|------|------|-----|-----|

| Bit No.  | 7     | 6   | 5       | 4 | 3    | 2    | 1   | 0   |

| Name     | SUD   |     |         |   | DA11 | DA10 | DA9 | DA8 |

SUD Simultaneous Update

- 1 Do not update D/A (hold off update of DAC0 until DAC1 is loaded)

- Normal operation. Update D/A when MSB is written

DA11 - 8 D/A bits 11 - 8 for output channel 0; DA11 is the MSB; D/A data is an unsigned 12-bit value.

| Base + 6 | Write | DAG | C 1 LSB |     |     |     |     |     |

|----------|-------|-----|---------|-----|-----|-----|-----|-----|

| Bit No.  | 7     | 6   | 5       | 4   | 3   | 2   | 1   | 0   |

| Name     | DA7   | DA6 | DA5     | DA4 | DA3 | DA2 | DA1 | DA0 |

# **Definitions:**

DA7 - 0 D/A data bits 7 - 0 for output channel 1; DA0 is the LSB; D/A data is an unsigned 12-bit value.

| Base + 7 | Write | DAC | C 1 MSB |   |      |      |     |     |

|----------|-------|-----|---------|---|------|------|-----|-----|

| Bit No.  | 7     | 6   | 5       | 4 | 3    | 2    | 1   | 0   |

| Name     |       |     |         |   | DA11 | DA10 | DA9 | DA8 |

DA11 - 8 D/A bits 11 - 8 for output channel 1; DA11 is the MSB; D/A data is an unsigned 12-bit value.

When this register is written, DAC 1 will be updated. If SUD is set in Base + 5, DAC 0 will also be updated.

# Base + 8 Write Clear Interrupt Request Flip Flop

Writing to this register clears the on-board interrupt flip flop. The value written does not matter.

The interrupt flip flop is set whenever an interrupt is generated on Diamond-MM-AT (i.e. during A/D conversions), and it must be cleared by software before another interrupt can be generated. Diamond-MM-AT's software driver includes an interrupt handler that performs this task automatically.

| Bit No. | 7   | 6    | 5  | 4    | 3     | 2     | 1     | 0     |

|---------|-----|------|----|------|-------|-------|-------|-------|

| Name    | STS | TINT | SD | AINT | ADCH3 | ADCH2 | ADCH1 | ADCH0 |

STS A/D chip status:

1 A/D conversion or scan is in progress

0 A/D is idle

TINT Timer interrupt request status:

1 Interrupt request has been generated by timer 0

0 No interrupt is pending from timer 0

SD Single-ended / Differential A/D input mode setting (readback of jumper setting):

1 Single-ended (default)

0 Differential

AINT Analog interrupt request status:

1 Interrupt request is pending from A/D circuit

0 No interrupt is pending from A/D circuit

ADCH3 - 0 Current A/D channel; this is the channel currently selected on board and is the channel that will be used for the next A/D conversion (unless a new value is written to the channel register before then). This data is not necessarily the same as the channel no. in the LSB of the next A/D data from the board.

# Base + 9 Read/Write Control Register

| Bit No. | 7     | 6 | 5 | 4 | 3     | 2     | 1     | 0      |

|---------|-------|---|---|---|-------|-------|-------|--------|

| Name    | AINTE |   |   |   | TINTE | DMAEN | CLKEN | CLKSEL |

AINTE Analog interrupt enable:

1 Enable A/D interrupts

0 Disable A/D interrupts

TINTE Timer interrupt enable:

1 Enable interrupts from timer 0

0 Disable interrupts from timer 0

DMAEN DMA enable (DMA operation is explained later in this manual):

1 Enable DMA operation

0 Disable DMA operation

CLKEN Enable hardware A/D clock:

1 Enable hardware trigger (source is selected with CLKSEL bit)

0 Disable hardware trigger

CLKSEL A/D clock select, used only when CLKEN = 1:

1 Internal trigger: on-board counter/timer (82C54) generates A/D conversions

O External trigger: DINO, pin 48 on I/O connector J3, generates A/D conversions

# Base + 10 Read/Write Counter/Timer and FIFO Control Register

| Bit No. | 7    | 6 | 5      | 4      | 3      | 2  | 1  | 0  |

|---------|------|---|--------|--------|--------|----|----|----|

| Name    | PAGE |   | FIFOEN | SCANEN | CLKFRQ | C2 | C1 | C0 |

## PAGE Page number for registers at Base + 12 through Base + 15

Page 0: 82C54 counter/timer access (normal operation)

Page 1: Calibration registers (not intended for direct access by the user)

## FIFOEN FIFO enable:

- 1 Enable FIFO operation; if interrupts are enabled, interrupts will occur when the FIFO is half full (HF = 1). This slows down the interrupt rate dramatically compared to the actual A/D sample rate.

- O Disable FIFO operation; if interrupts are enabled, interrupts will occur after each A/D conversion.

## SCANEN Scan enable:

- Scan mode enabled; FIFO will fill up with data for a single scan, and STS will stay high until an entire scan is complete; if interrupts are enabled, interrupts will occur on integral multiples of scans.

- O Scan mode disabled; The STS bit will correspond directly to the status indicator from the A/D converter

# CLKFRQ Clock frequency for counter/timer 1 input

- 0 10MHz

- 1 1MHz

## C2 External Clock Gate Enable

- 1 IN0- (pin 29 on the I/O header J3) acts as a gate for A/D sample control when external A/D clock is enabled (CLKSEL = 0). When IN0- is high, falling edges on DI0 (pin 48 on J3) will initiate A/D conversions. When IN0- is low, the DI0 signal is inhibited. IN0- is connected to a 10K $\Omega$  pull-up resistor.

- 0 IN0- does not act as a gate for external A/D clocking.

# C1 Counter 0 input source:

- 1 Input is a 100kHz on-board reference frequency derived from the 10MHz oscillator. INO- (pin 29 on the I/O header) gates this signal. When it is high (default), the 100kHz signal runs. When it is low, the 100kHz signal is stopped.

- Input is INO- (pin 29 on the I/O connector) inverted. Counter 0 counts on rising edges of INO-. INO- is connected to an on-board pull-up resistor, so only a connection to ground is necessary to toggle it.

# C0 Counters 1 and 2 gate control:

- Counters 1 and 2 are gated by DIN0 (pin 48 on the I/O connector). When DIN0 is high, the counters run; when DI0 is low, the counters are stopped. In this way pin 48 can be used as an A/D conversion gate signal when the counters are used for A/D conversion timing.

- O Counters 1 and 2 run freely with no gating.

# Base + 11 Write Analog Configuration Control Register

Bit No. Name

| 7 | 6 | 5 | 4 | 3     | 2    | 1  | 0  |

|---|---|---|---|-------|------|----|----|

|   |   |   |   | RANGE | ADBU | G1 | G0 |

RANGE 5V or 10V A/D positive full-scale range

ADBU A/D bipolar / unipolar setting; 0 = bipolar, 1 = unipolar

The table below lists the effects of the various combinations of ADBU and RANGE:

| RANGE | ADBU | A/D full-scale range |

|-------|------|----------------------|

| 0     | 0    | ±5V                  |

| 0     | 1    | 0 - 10V              |

| 1     | 0    | ±10V                 |

| 1     | 1    | Invalid setting      |

|       |      |                      |

# G1 - 0 A/D gain setting:

| G1 | G0 | Gain |

|----|----|------|

| 0  | 0  | 1    |

| 0  | 1  | 2    |

| 1  | 0  | 4    |

| 1  | 1  | 8    |

The gain setting is the ratio between the A/D full-scale range and the effective input signal range. Gain may be thought of as either amplifying the input signal to fit the A/D input range better, or dividing the A/D input range to create a smaller full-scale input range. For example, if the A/D input range is 0 - 10V, a gain setting of 2 creates an input signal range of 0 - 5V, and a gain setting of 4 creates an input signal range of 0 - 2.5V.

- $\Rightarrow$ : On power up or system reset, the board is configured for A/D bipolar mode, input range  $\pm 5V$ , gain = 1 (all bits set to 0).

- ⇒: Not all combinations of bits are valid. Please see the complete list of bit settings and corresponding input ranges on page 22.

Base + 11 Read Analog and Status Readback Register

| Bit No. | 7    | 6   | 5  | 4  | 3     | 2    | 1  | 0  |

|---------|------|-----|----|----|-------|------|----|----|

| Name    | WAIT | OVF | HF | EF | RANGE | ADBU | G1 | G0 |

This address provides a means of reading back the values written to the control register at Base + 11 along with FIFO and scan status signals.

WAIT Indicates that the analog input circuit is settling on a new value. This signal goes high whenever the user writes to register 2 (channel address register) or register 11 (analog configuration register). The duration of the WAIT period is 10uS, which is the settling time required for the analog input circuit.

OVF FIFO overflow flag; 0 = no overflow; 1 = overflow

HF FIFO half full flag; 0 = FIFO is less than half full; 1 = FIFO is at least half full

EF FIFO empty flag; 0 = FIFO is not empty; 1 = FIFO is empty

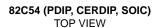

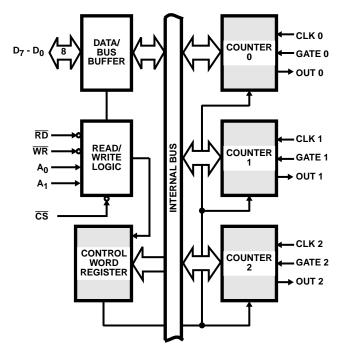

# PAGE 0: 82C54 Counter/Timer

# Base + 12 through Base + 15 Read/Write

# 82C54 Counter/Timer Registers

These registers map directly to the on-board 82C54 counter/timer IC used for A/D conversion timing and user functions. The definitions of these registers can be found in the 82C54 datasheet appended to the back of this manual.

# Page 1: Calibration Control Registers

These register descriptions are provided for completeness. In most applications the programmer does not need to access them directly. Erroneous use of these registers can result in putting the board out of calibration.

Base + 12 Read/Write EEPROM / TrimDAC Data Register

| Bit No. | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Name    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

D7-0 Calibration data to be read or written to the EEPROM and/or TrimDAC.

During EEPROM or TrimDAC write operations, the data written to this register will be written to the selected device.

During EEPROM read operations this register contains the data to be read from the EEPROM and is valid after EEBUSY = 0 (bit 5 in register 14).

The TrimDAC data cannot be read back.

Base + 13 Read/Write EEPROM / TrimDAC Address Register

| Bit No. | 7 | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|---|----|----|----|----|----|----|----|

| Name    |   | A6 | A5 | A4 | А3 | A2 | A1 | A0 |

A6-A0 EEPROM / TrimDAC address. The EEPROM only recognizes address 0 – 127. The TrimDAC only recognizes addresses 0 – 7. Writing to an address beyond the recognized range will result in only the significant bits being accepted. For example, when accessing the EEPROM, selecting address 129 is the same as selecting address 1 (dropping address bit 7).

# Base + 14 Write Calibration Control Register

| Bit No. | 7     | 6     | 5       | 4      | 3      | 2 | 1 | 0 |

|---------|-------|-------|---------|--------|--------|---|---|---|

| Name    | EE_EN | EE_RW | LOADCAL | CMUXEN | TDACEN |   |   |   |

This register is used to access the EEPROM and TrimDAC during board calibration.

Do not access this register unless you have a clear understanding of what you are doing, as you may destroy calibration values and prevent the board from being autocalibrated without user intervention. If you have any questions please contact Technical Support first at support@diamondsystems.com.

CMUXEN Calibration multiplexor enable:

1 = enable cal mux and disable regular input muxes

0 = disable cal mux

When CMUXEN = 1, the analog input channels 0-15 are disabled, and the calibration multiplexor channels 0-7 may be read as analog input channels 16-23. The cal mux input channels are connected to low-drift analog voltages that are used to calibrate the analog input circuit. Two of the input channels are the two DACs, so they may be calibrated as well.

EE\_EN EEPROM Enable. When this bit is set, a Read/Write command to the EEPROM will be processed. Read or Write is indicated by the EE\_RW bit. Once this bit is set, the program must monitor EEBUSY (see next page)and wait until it is 0.

EE\_RW Determines the direction of the EEPROM command. 0 = Write, 1 = Read.

LOADCAL Load Calibration. Setting this bit causes the EEPROM values in locations 0 – 7 to be transferred to the TrimDAC (forces a reloading of the default calibration values).

TDACEN TrimDAC Enable – writes the data in register 12 to the TrimDAC no. indicated by A2 – A0 in register 13. Data may not be read from the TrimDACs, so there is no read/write bit for this operation. Once this bit is set, the program must monitor TDBUSY (see next page)and wait until it is 0.

Note: EE\_EN and TDACEN must not be set at the same time.

| libration Status Register |

|---------------------------|

| I                         |

| Bit No. | 7 | 6      | 5      | 4      | 3 | 2 | 1 | 0 |

|---------|---|--------|--------|--------|---|---|---|---|

| Name    | 0 | TDBUSY | EEBUSY | CMUXEN | 0 | 0 | 0 | 0 |

# TDBUSY TrimDAC busy indicator

- 0 User may access TrimDAC or perform another operation

- 1 TrimDAC is being accessed; user must wait

# EEBUSY EEPROM busy indicator

- 0 EEPROM is idle; user may access it or perform another operation

- 1 EEPROM access cycle is in progress; user must wait

The TrimDAC requires about 0.5ms to execute a single complete read or write cycle.

# Base + 15 Write EEPROM Access Key Register

The user must write the value 0xA5 (binary 10100101) to this register in order to get access to the EEPROM. This helps prevent accidental corruption of the EEPROM contents. This register must be written to each time the PAGE bit is set to 1, as it is cleared when the PAGE bit is set to 0.

#### Base + 15 Read FPGA Revision Code

This register may be read back to indicate the revision level of the FPGA design.

# 7. ANALOG INPUT RANGES AND RESOLUTION

## 7.1 Resolution

Diamond-MM-AT uses a 12-bit A/D converter. This means that the analog input voltage can be measured to the precision of a 12-bit binary number. The maximum value of a 12-bit binary number is  $2^{12}$  - 1, or 4095, so the full range of numerical values that you can get from a Diamond-MM-AT analog input channel is 0 - 4095.

The smallest change in input voltage that can be detected is  $1/(2^{12})$ , or 1/4096, of the full-scale input range. This smallest change results in an increase or decrease of 1 in the A/D code, and so this change is referred to as 1 LSB, or 1 least significant bit.

# 7.2 Unipolar and Bipolar Inputs

Diamond-MM-AT can measure both unipolar (positive only) and bipolar (positive and negative) analog voltages. In general you should select the highest gain you can that will allow the A/D converter to read the full range of voltages over which your input signals will vary. However, if you pick too high a gain, then the A/D converter will clip at either the high end or low end, and you will not be able to read the full range of voltages on your input signals.

# 7.3 Single Ended and Differential Inputs

Diamond-MM-AT can handle both single-ended and differential inputs. A single-ended input is a single-wire input that is referenced to analog ground on the board. This means that the input voltage will be measured with respect to the board's analog ground. A differential input is a two-wire input, and the board will measure the difference between the voltages of the two inputs. Polarity is important for a differential input. Diamond-MM-AT will subtract the voltage on the low input (- pin) from the voltage of the high input (+ pin). Differential inputs are frequently used when the grounds of the input device and the measurement device (Diamond-MM-AT) are at different voltages, or when a low-level signal is being measured that has its own ground wire.

# 8. ANALOG INPUT RANGE SETTINGS

The table below lists all the valid analog input ranges on Diamond-MM-AT. Although there are 16 possible combinations for the 4 range control bits, only 12 configurations are valid due to the configuration of the A/D converter.

There is some overlap in the meaning of the bit combinations, so the total number of unique input ranges is 9.

The control bits RANGE, ADBU, G1, and G0 are in the control register at Base + 11.

# **Diamond-MM-AT Analog Input Ranges**

| Range No. | RANGE | ADBU | G1 | G0 | Input Range | 1 LSB   |

|-----------|-------|------|----|----|-------------|---------|

| 0         | 0     | 0    | 0  | 0  | ±5V         | 2.44mV  |

| 1         | 0     | 0    | 0  | 1  | ±2.5V       | 1.22mV  |

| 2         | 0     | 0    | 1  | 0  | ±1.25V      | 0.61mV  |

| 3         | 0     | 0    | 1  | 1  | ±0.625V     | 0.305mV |

| 4         | 0     | 1    | 0  | 0  | 0-10V       | 2.44mV  |

| 5         | 0     | 1    | 0  | 1  | 0-5V        | 1.22mV  |

| 6         | 0     | 1    | 1  | 0  | 0-2.5V      | 0.61mV  |

| 7         | 0     | 1    | 1  | 1  | 0-1.25V     | 0.305mV |

| 8         | 1     | 0    | 0  | 0  | ±10V        | 4.88mV  |

| 9         | 1     | 0    | 0  | 1  | ±5V         | 2.44mV  |

| 10        | 1     | 0    | 1  | 0  | ±2.5V       | 1.22mV  |

| 11        | 1     | 0    | 1  | 1  | ±1.25V      | 0.61mV  |

| 12        | 1     | 1    | 0  | 0  | INVA        | LID     |

| 13        | 1     | 1    | 0  | 1  | INVA        | LID     |

| 14        | 1     | 1    | 1  | 0  | INVA        | LID     |

| 15        | 1     | 1    | 1  | 1  | INVA        | LID     |

#### 9. PERFORMING AN A/D CONVERSION

This chapter describes the steps involved in performing an A/D conversion on a selected input channel using direct programming (not with the driver software).

There are five steps involved in performing an A/D conversion:

- 1. Select the input channel

- 2. Select the input range (if a new range is desired)

- 3. Perform an A/D conversion on the current channel

- 3. Wait for the conversion to finish

- 4. Read the data

- 5. Convert the numerical data to a meaningful value

# 9.1 Select the input channel

To select the input channel to read, write a low-channel/high-channel pair to the channel register at Base + 2. The low 4 bits select the low channel, and the high 4 bits select the high channel. When you write any value to this register, the current A/D channel is set to the low channel.

When you perform an A/D conversion, the current channel is automatically incremented to the next channel in the selected range. Therefore, to perform A/D conversions on a group of consecutively-numbered channels, you do not need to write the input channel prior to each conversion. For example, to read from channels 0 - 2, write Hex 20 to Base + 2. The first conversion is on channel 0, the second will be on channel 1, and the third will be on channel 2. Then the channel counter wraps around to the beginning again, so the fourth conversion will be on channel 0 again. This sequence will repeat until you change the settings at Base + 2 or reset the board.

About 10 microseconds is required as a settling time for the analog front end circuitry after you select the channel. If you are not selecting a new analog input range, you must wait for this settling time by monitoring the WAIT bit before starting the A/D conversion. Wait for WAIT = 0 before proceeding. If you are selecting a new input range, you may do this before waiting.

#### 9.2 Select the input range

To select a new input range, write the desired setting to the register at Base + 11 (see page 17). If you want to use the same range as the previous A/D conversion, you can skip this step.

About 10 microseconds is required as a settling time for the analog front end circuitry after you select the input range. Monitor the WAIT bit (Base + 11 bit 7) before starting the A/D conversion. Wait for WAIT = 0 before proceeding.

#### Valid input channel / range sequences:

A. Select new input channel settings and new input range

Select input channel range with Base + 2; channel is set to low channel no.

Select input range with Base + 11

Wait for WAIT = 0 in Base + 11

B. Select new input channel, use same input range

Select input channel range with Base + 2; channel is set to low channel no.

Wait for WAIT = 0 in Base + 11

C. Use current settings with autoincrement of input channel

<No steps required>

#### 9.3 Perform an A/D conversion on the current channel

After writing to the channel register and waiting for the analog circuitry to settle, you can perform an A/D conversion on the selected channel. To do this, simply write to base + 0 to start the conversion. The data value does not matter and is ignored.

# 9.4 Wait for the conversion to finish

The A/D converter takes up to 10 microseconds to complete a conversion. Most processors and software can operate fast enough so that if you try to read the A/D converter immediately after writing to base + 0, you will beat the A/D converter and get invalid data. Therefore the A/D converter provides a status signal STS to indicate whether it is busy or idle. This bit can be read back as bit 7 in the status register at Base + 8. When the A/D converter is busy (performing an A/D conversion), this bit is 1, and when the A/D converter is idle (conversion is done and data is available), this bit is 0. You must wait for STS = 0 before reading A/D data.

## 9.5 Read the data

Once the conversion is complete, you can read the data back from the A/D converter. The data is 12 bits wide and is read back in two 8-bit bytes. The LSB must be read first, followed by the MSB. Refer to the register definitions on p. 8 for the format of the A/D data. The following pseudocode illustrates how to construct the 12-bit A/D value from these two bytes:

```

LSB = read(base) / 16 ; shift LSB right 4 bits, delete channel #

MSB = read(base+1) * 16 ; shift MSB left 4 bits

Data = MSB + LSB ; combine the 2 bytes into a 12-bit value

```

The final data ranges from 0 to 4095 (0 to  $2^{12}$  - 1).

A/D data before manipulation:

|      | Base + 1 |     |     |     |     |     |               | Base + 0 |     |     |     |     |     |     |     |

|------|----------|-----|-----|-----|-----|-----|---------------|----------|-----|-----|-----|-----|-----|-----|-----|

| 7    | 6        | 5   | 4   | 3   | 2   | 1   | 0 7 6 5 4 3 2 |          |     |     |     |     |     | 1   | 0   |

| AD11 | AD10     | AD9 | AD8 | AD7 | AD6 | AD5 | AD4           | AD3      | AD2 | AD1 | AD0 | СНЗ | CH2 | CH1 | CH0 |

A/D data after manipulation:

|   | MSB |   |   |      |      |     |     | LSB         |     |     |     |     |     |     |     |

|---|-----|---|---|------|------|-----|-----|-------------|-----|-----|-----|-----|-----|-----|-----|

| 7 | 6   | 5 | 4 | 3    | 2    | 1   | 0   | 7 6 5 4 3 2 |     |     |     |     |     | 1   | 0   |

| 0 | 0   | 0 | 0 | AD11 | AD10 | AD9 | AD8 | AD7         | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 |

## 9.6 Convert the numerical data to a meaningful value

Once you have the A/D value, you need to convert it to a meaningful value. The first step is to convert it back to the actual measured voltage. Afterwards you may need to convert the voltage to some other engineering units (for example, the voltage may come from a temperature sensor, and then you would need to convert the voltage to the corresponding temperature according to the temperature sensor's characteristics). Since there are a large number of possible input devices, this secondary step is not included here; only conversion to input voltage is described.

To convert the A/D value to the corresponding input voltage, use the following formulas:

Conversion Formula for Unipolar Input Ranges:

# Input voltage = (A/D value / 4096) \* Full-scale input range

Example: Input range is 0-5V and A/D value is 1776: Input voltage = 1776 / 4096 \* 5V = 2.168V

Here is an illustration of the relationship between A/D code and input voltage for a unipolar input range ( $V_{FS}$  = Full scale input voltage):

| A/D Code | Input voltage                                         |

|----------|-------------------------------------------------------|

| 0        | 0V                                                    |

| 1        | 1 LSB (V <sub>FS</sub> / 4096)                        |

| 2048     | V <sub>FS</sub> / 2                                   |

| 2049     | V <sub>FS</sub> / 2 + 1 LSB                           |

| 4095     | V <sub>FS</sub> - 1 LSB (e.g. 4.9988V for 0-5V range) |

Conversion Formula for Bipolar Input Ranges:

Example: Input range is  $\pm 5V$  and A/D value is 1776: Input voltage = 1776 / 2048 \* 5V - 5V = -0.664V

Here is an illustration of the relationship between A/D code and input voltage for a bipolar input range ( $V_{FS}$  = Full scale input voltage):

| A/D Code | Input voltage                            |            |

|----------|------------------------------------------|------------|

| 0        | -V <sub>FS</sub>                         |            |

| 1        | -V <sub>FS</sub> + 1 LSB                 |            |

| 2047     | -1 LSB                                   |            |

| 2048     | 0V                                       |            |

| 2049     | +1 LSB                                   |            |

| 4095     | $V_{FS}$ - 1 LSB (e.g. 4.9976V for $\pm$ | ±5V range) |

# 10. A/D SCAN, INTERRUPT, AND FIFO OPERATION

Three control bits determine the behavior of DMM-AT during A/D conversions.

**SCANEN** (scan enable, Base + 10 bit 4): A/D conversions may be performed one at a time or in scan mode. In non-scan mode, each A/D start command (software or external clock) causes the current channel to be sampled, and the internal channel register to increment to the next channel in the selected range. In scan mode, each A/D start command causes all the channels in the selected range to be sampled once in quick succession.

**FIFOEN** (FIFO enable, Base + 10 bit 5): The FIFO affects interrupt behavior. If the FIFO is not enabled, then each A/D start command will result in an interrupt at the end of the sample or scan. If the FIFO is enabled, then the interrupt will occur once the FIFO reaches its threshold (half full, or 256 samples). If interrupts are not enabled, then FIFOEN has no effect on the board's behavior. In all cases, at the end of an A/D conversion A/D data is latched into the FIFO. Data is read out of the FIFO with 2 read operations, the LSB and channel tag from Base + 0 and the MSB from Base + 1. This is true even when FIFOEN = 0.

**AINTE** (analog input interrupt enable, Base + 9 bit 7): This bit enables interrupt operation. The board will generate an interrupt when the appropriate set of conditions occur based on the SCANEN and FIFOEN bits. The interrupt routine (included in the Diamond Systems Universal Driver software or else provided by the programmer) reads A/D data out of the FIFO.

For all cases where AINTE = 1, CLKEN must also be set to 1 to enable hardware A/D clocking. This is because when interrupt operation is enabled, A/D conversions cannot be triggered by software and must be triggered by a hardware source.

| AINTE | FIFOEN | SCANEN | Operation                                                                                                                                                                |

|-------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0      | 0      | Single A/D conversions are triggered by write to B+0.                                                                                                                    |

|       |        |        | WAIT = STS.                                                                                                                                                              |

|       |        |        | No interrupt occurs.                                                                                                                                                     |

|       |        |        | The user program monitors STS or WAIT and reads A/D data when it goes low.                                                                                               |

| 0     | 0      | 1      | A/D Scans are triggered by write to B+0. All channels between LOW and HIGH will be sampled.                                                                              |

|       |        |        | WAIT goes high at the first STS high pulse and stays high until the last STS pulse goes low.                                                                             |

|       |        |        | No interrupt occurs.                                                                                                                                                     |

|       |        |        | The user program monitors WAIT and reads the A/D data after it goes low.                                                                                                 |

| 0     | 1      | 0      | Same operation as case 000 above.                                                                                                                                        |

| 0     | 1      | 1      | Same operation as case 001 above.                                                                                                                                        |

| 1     | 0      | 0      | Single A/D conversions are triggered by either TM_OUT2 or DIN0, depending on the value of INTTRIG.  WAIT = STS.                                                          |

|       |        |        | INT goes high after each conversion is done (when STS goes low).                                                                                                         |

|       |        |        | The interrupt routine reads one A/D sample each time it runs.                                                                                                            |

| 1     | 0      | 1      | A/D scans are triggered by either TM_OUT2 or DI0, depending on the value of INTTRIG.                                                                                     |

|       |        |        | WAIT goes high at the first STS high pulse and stays high until the last STS pulse goes low.                                                                             |

|       |        |        | INT goes high after the last STS pulse goes low (i.e. when WAIT goes low).                                                                                               |

|       |        |        | The interrupt routine reads out one entire A/D scan each time it runs.                                                                                                   |

| 1     | 1      | 0      | Single A/D conversions are triggered by either TM_OUT2 or DIN0, depending on the value of INTTRIG.  WAIT = STS.                                                          |

|       |        |        | INT goes high when HF goes high.                                                                                                                                         |

|       |        |        | The interrupt routine reads out 256 samples (half the FIFO) each time                                                                                                    |

|       |        |        | it runs.                                                                                                                                                                 |

| 1     | 1      | 1      | A/D scans are triggered by either TM_OUT2 or DI0, depending on the value of INTTRIG.                                                                                     |

|       |        |        | WAIT goes high at the first STS high pulse and stays high until the last STS pulse goes low.                                                                             |

|       |        |        | INT goes high after the last STS pulse goes low (i.e. when WAIT goes low) AND HF is high (i.e. an integral no. of scans has occurred and the FIFO is half full or more). |

|       |        |        | The interrupt routine reads out enough complete scans to equal 256 or more samples each time it runs.                                                                    |

## 11. ANALOG OUTPUT RANGES AND RESOLUTION

# 11.1 Description

Diamond-MM-AT uses a two-channel 12-bit D/A converter (DAC) to provide two analog outputs. A 12-bit DAC can generate output voltages with the precision of a 12-bit binary number. The maximum value of a 12-bit binary number is  $2^{12}$  - 1, or 4095, so the full range of numerical values that you can write to the analog outputs on Diamond-MM-AT is 0 - 4095.

The DACs on Diamond-MM-AT operate in both unipolar and bipolar modes. The user can select from an on-board fixed 5V reference for 0-10V and  $\pm$ 5V ranges, or an on-board programmable reference for custom ranges. In addition two pins on the I/O connector enable the user to provide an external reference for the DACs.

In most cases each DAC can be set to a different range. The only exception is that if both DACs are using the programmable range, then both DACs must be set to the same polarity (unipolar or bipolar mode).

$\Rightarrow$  **Note:** In this manual, the terms analog output, D/A, and DAC are all used interchangeably to mean the same thing.

#### 11.2 Resolution

The *resolution* is the smallest possible change in output voltage. For a 12-bit DAC the resolution is  $1/(2^{12})$ , or 1/4096, of the full-scale output range. This smallest change results from an increase or decrease of 1 in the D/A code, and so this change is referred to as 1 LSB, or 1 least significant bit. The value of this LSB is calculated as follows:

# 1 LSB = Full-scale output voltage / 4096

Example: Full-scale output voltage = 10V (for 0-10V or  $\pm$ 5V ranges) 1 LSB = 10V / 4096 = 2.44mV

# 11.3 Full-Scale Voltage Selection

Jumper block J5 in the middle of the board is used for DAC configuration. The left group of 5 pairs of pins controls DAC 0, and the right group of 5 pins controls DAC 1. Configuration is done according to the instructions below.

| Position | Function                                                        |

|----------|-----------------------------------------------------------------|

| 5        | Selects 5V reference (if N jumper is installed)                 |

| Р        | Selects programmable reference (if N jumper is installed)       |

| N        | Selects internal reference, 5 or P above                        |

| X        | Selects external reference, pin 26 for DAC 0 or pin 28 for DAC1 |

| В        | Selects bipolar mode if in, unipolar mode if out                |

For each DAC, one jumper must be installed in either N or X but not both.

For each DAC, if a jumper is installed in N, then one jumper must be installed in either 5 or P but not both.

If both DACs are set to P and N (internal programmable reference), then both DACs must have the same B jumper setting (in for both or out for both).

## 12. GENERATING AN ANALOG OUTPUT

This chapter describes the steps involved in generating an analog output (also called performing a D/A conversion) on a selected output channel using direct programming (not with the driver software).

There are two steps involved in performing a D/A conversion:

- 1. Compute the D/A output value for the desired output voltage

- 2. Write the value to the selected output channel

# 12.1 Compute the D/A code for the desired output voltage

Use the following formulas to compute the D/A code required to generate the desired voltage:

For Unipolar operation:

# Output value = Desired output voltage / Full-scale voltage \* 4096

```

Example: Desired output voltage = 2.168V, full-scale voltage = 10V (0-10V range)

Output code = 2.168 / 5 * 4096 = 1776

```

#### For Bipolar operation:

# Output value = Desired output voltage / Full-scale voltage \* 2048 + 2048

```

Example: Desired output voltage = -3.0V, full-scale voltage = 5V (\pm 5V range)

Output code = -3.0 / 5 * 2048 + 2048 = 819 (rounded to nearest integer value)

```

⇒ **Note:** The DAC cannot generate the actual full-scale reference voltage; to do so would require an output code of 4096, which is not possible with a 12-bit number. The maximum output value is 4095. Therefore the maximum possible output voltage is 1 LSB less than the full-scale reference voltage.

## 12.2 Write the value to the selected output channel

The two DACs are located at addresses base + 4 through base + 7 (see Chapter 6, I/O Map). Each DAC uses one pair of addresses. First write the LSB to the lower address, then write the MSB to the upper address. Writing the MSB to a DAC causes that DAC to be updated, outputting the new voltage.

First use the following formulas to compute the LSB and MSB values:

# LSB = D/A Code AND 255 ;keep only the low 8 bits

# MSB = int(D/A code / 256) ;strip off low 8 bits, keep 4 high bits

```

Example: Output code = 1776

LSB = 1776 AND 255 = 240 (F0 Hex); MSB = int(1776 / 256) = int(6.9375) = 6

(In other words, 1776 = 6*256 + 240)

```

Note that the LSB does not actually need to be computed, since Diamond-MM-AT uses an 8-bit databus and will ignore the high byte if a program attempts to write a 16-bit word to it.

Now write these values to the selected channel:

```

For Channel 0: Write 240 to base + 4, then write 6 to base + 5, updating Channel 0 For Channel 1: Write 240 to base + 6, then write 6 to base + 7, updating Channel 1

```

#### 13. DIGITAL I/O OPERATION

Diamond-MM-AT contains an 8-bit digital output port and an 8-bit digital input port. Both ports are located at base + 3. To access the output lines, simply write an 8-bit value to base + 3. Similarly, to read the input lines, read from base + 3.

The output lines are located at pins 33 through 40 on the I/O header J3 (see p. 4). They use a 74FCT273 chip. They do not have a readback feature, so your program must keep track of the latest output value.

The inputs are located at pins 41 through 48 on the I/O header J3. They are CMOS/TTL compatible. There is no latch signal provided. However, the values are latched when being read to prevent transitions during the CPU read operation. All lines have  $10K\Omega$  pull-up resistors.

Input line 2 doubles as the gate control for counter 0. When it is high, counter 0 can count, and when it is low, counter 0 holds its present value.

Input line 0 doubles as a programmable gate control for counters 1 and 2. These counters are combined together and used as the A/D pacer clock. Bit 0 of the counter/timer control register at base + 10 determines whether these counters run freely or whether Input line 0 is the gate (see Chapter 6, page 13).

# **Digital I/O Specifications:**

No. of inputs 8, HCT/TTL compatible

Input voltage Logic 0: 0.0V min, 0.8V max; Logic 1: 2.0V min, 5.0V max

No. of outputs 8, FCT/TTL compatible

Output voltage Logic 0: 0.0V min, 0.33V max; Logic 1: 3.8V min, 5.0V max

Output current Logic 0: +64mA max per line; Logic 1: -15mA max per line

#### 14. SPECIFICATIONS

**Analog Inputs**

No. of inputs 8 differential or 16 single-ended (user selectable)

A/D resolution 12 bits (1/4096 of full scale)

Input ranges Bipolar:  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$ ,  $\pm 1V$ ,  $\pm 0.5V$ , Custom

Unipolar: 0-10V, 0-5V, 0-2.5V, 0-1V, Custom

Input bias current 50nA max

Maximum input voltage  $\pm 10V$  for linear operation

Overvoltage protection ±35V on any analog input without damage

Nonlinearity  $\pm 1$ LSB, no missing codes

Conversion rate 100,000 samples per second max (with DMA operation)

Conversion trigger software trigger, internal pacer clock, or external TTL signal

**Autocalibration**

Circuits calibrated A/D (all 9 input ranges) and D/A A/D error after calibration  $\pm 1$ LSB (typical),  $\pm 2$ LSB (max)  $\pm 1$ LSB (typical),  $\pm 2$ LSB (max)

**Analog Outputs**

No. of outputs 2

D/A resolution 12 bits (1/4096 of full scale)

Output ranges 0-10V, ±5V, adjustable, or external reference input

Output current  $\pm 8$ mA max per channel Settling time  $\pm 4\mu$ S max to  $\pm 1/2$  LSB

Relative accuracy  $\pm 1$  LSB

Nonlinearity ±1 LSB, monotonic

Digital I/O

No. of inputs 8, HCT/TTL compatible

Input voltage Logic 0: 0.0V min, 0.8V max; Logic 1: 2.0V min, 5.0V max

No. of outputs 8, HCT/TTL compatible

Output voltage Logic 0: 0.0V min, 0.33V max; Logic 1: 3.8V min, 5.0V max Output current Logic 0: +64mA max per line; Logic 1: -15mA max per line

Counter/Timers

A/D Pacer clock 32-bit down counter (2 82C54 counters cascaded)

Clock source 10MHz on-board clock source or external signal

General purpose 16-bit down counter (1 82C54 counter)

General

Power supply +5VDC  $\pm 10\%$ Current consumption 220mA typical

I/O header output current ±15V: ±10mA max with DACs unloaded

+5V: Depends on PC/104 power supply

Power supply outputs are not short-circuit protected!

Operating temperature -40 to +85°C

Operating humidity 5% to 95% noncondensing

PC/104 bus 8 bits

March 1997

# **CMOS Programmable Interval Timer**

# **Features**

- 8MHz to 12MHz Clock Input Frequency

- Compatible with NMOS 8254

- Enhanced Version of NMOS 8253

- Three Independent 16-Bit Counters

- Six Programmable Counter Modes

- · Status Read Back Command

- Binary or BCD Counting

- Fully TTL Compatible

- Single 5V Power Supply

- Low Power

| Operating Temperature Penges |                |

|------------------------------|----------------|

| - ICCOP10mA at               | 8MHz           |

| - ICCSB                      | . <b>10</b> μΑ |

Operating Temperature Ranges

| - | C82C54 | 0°C to +70°C   |

|---|--------|----------------|

| - | 182C54 | 40°C to +85°C  |

| _ | M82C54 | 55°C to +125°C |

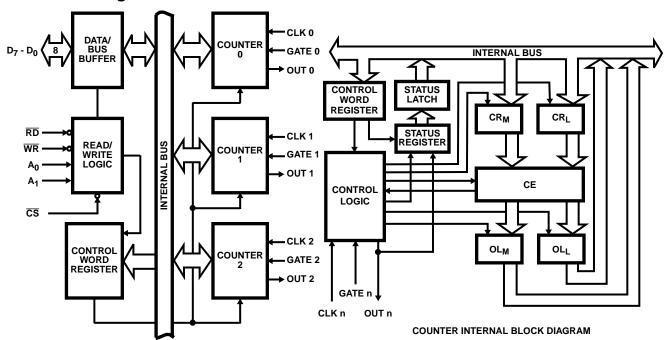

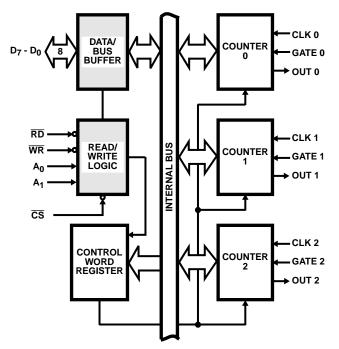

# Description

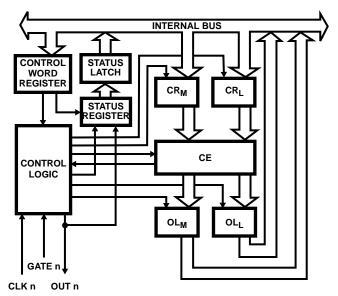

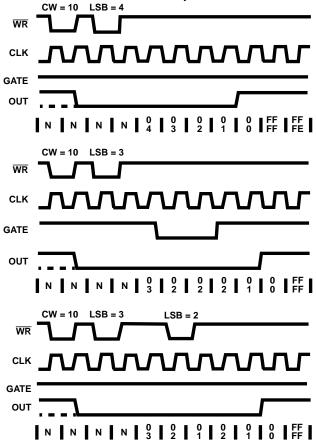

The Harris 82C54 is a high performance CMOS Programmable Interval Timer manufactured using an advanced 2 micron CMOS process.

The 82C54 has three independently programmable and functional 16-bit counters, each capable of handling clock input frequencies of up to 8MHz (82C54) or 10MHz (82C54-10) or 12MHz (82C54-12).

The high speed and industry standard configuration of the 82C54 make it compatible with the Harris 80C86, 80C88, and 80C286 CMOS microprocessors along with many other industry standard processors. Six programmable timer modes allow the 82C54 to be used as an event counter, elapsed time indicator, programmable one-shot, and many other applications. Static CMOS circuit design insures low power operation.

The Harris advanced CMOS process results in a significant reduction in power with performance equal to or greater than existing equivalent products.

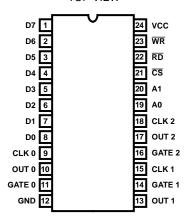

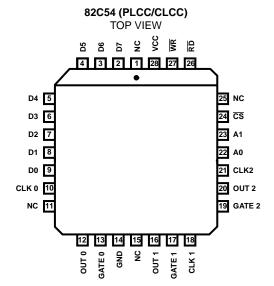

## **Pinouts**

# **Ordering Information**

|                 | PART NUMBERS | 3            | TEMPERATURE     |                |          |

|-----------------|--------------|--------------|-----------------|----------------|----------|

| 8MHz            | 10MHz        | 12MHz        | RANGE           | PACKAGE        | PKG. NO. |

| CP82C54         | CP82C54-10   | CP82C54-12   | 0°C to +70°C    | 24 Lead PDIP   | E24.6    |

| IP82C54         | IP82C54-10   | IP82C54-12   | -40°C to +85°C  | 24 Lead PDIP   | E24.6    |

| CS82C54         | CS82C54-10   | CS82C54-12   | 0°C to +70°C    | 28 Lead PLCC   | N28.45   |

| IS82C54         | IS82C54-10   | IS82C54-12   | -40°C to +85°C  | 28 Lead PLCC   | N28.45   |

| CD82C54         | CD82C54-10   | CD82C54-12   | 0°C to +70°C    | 24 Lead CERDIP | F24.6    |

| ID82C54         | ID82C54-10   | ID82C54-12   | -40°C to +85°C  | 24 Lead CERDIP | F24.6    |

| MD82C54/B       | MD82C54-10/B | MD82C54-12/B | -55°C to +125°C | 24 Lead CERDIP | F24.6    |

| MR82C54/B       | MR82C54-10/B | MR82C54-12/B | -55°C to +125°C | 28 Lead CLCC   | J28.A    |

| SMD # 8406501JA | -            | 8406502JA    | -55°C to +125°C | 24 Lead CERDIP | F24.6    |

| SMD# 84065013A  | -            | 84065023A    | -55°C to +125°C | 28 Lead CLCC   | J28.A    |

| CM82C54         | CM82C54-10   | CM82C54-12   | 0°C to +70°C    | 24 Lead SOIC   | M24.3    |

# Functional Diagram

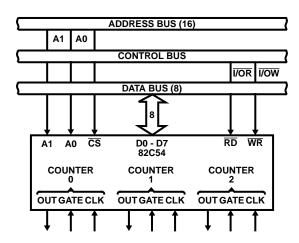

# Pin Description

| SYMBOL  | DIP PIN<br>NUMBER | TYPE | DEFINITION                                                                     |

|---------|-------------------|------|--------------------------------------------------------------------------------|

| D7 - D0 | 1 - 8             | I/O  | DATA: Bi-directional three-state data bus lines, connected to system data bus. |

| CLK 0   | 9                 | I    | CLOCK 0: Clock input of Counter 0.                                             |

| OUT 0   | 10                | 0    | OUT 0: Output of Counter 0.                                                    |

| GATE 0  | 11                | I    | GATE 0: Gate input of Counter 0.                                               |

| GND     | 12                |      | GROUND: Power supply connection.                                               |

| OUT 1   | 13                | 0    | OUT 1: Output of Counter 1.                                                    |

| GATE 1  | 14                | I    | GATE 1: Gate input of Counter 1.                                               |

| CLK 1   | 15                | I    | CLOCK 1: Clock input of Counter 1.                                             |

| GATE 2  | 16                | I    | GATE 2: Gate input of Counter 2.                                               |

| OUT 2   | 17                | 0    | OUT 2: Output of Counter 2.                                                    |

# Pin Description (Continued)

| SYMBOL          | DIP PIN<br>NUMBER | TYPE |                                                       |                                                                                                                                                        | DEFINITION                      | ı                                                                              |  |

|-----------------|-------------------|------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------|--|

| CLK 2           | 18                | I    | CLOCK 2: C                                            | lock input of                                                                                                                                          | Counter 2.                      |                                                                                |  |

| A0, A1          | 19 - 20           | I    |                                                       | ADDRESS: Select inputs for one of the three counters or Control Word Register for read/write operations. Normally connected to the system address bus. |                                 |                                                                                |  |

|                 |                   |      | A1                                                    | A0                                                                                                                                                     | SELECTS                         | 7                                                                              |  |

|                 |                   |      | 0                                                     | 0                                                                                                                                                      | Counter 0                       |                                                                                |  |

|                 |                   |      | 0                                                     | 1                                                                                                                                                      | Counter 1                       | 7                                                                              |  |

|                 |                   |      | 1                                                     | 0                                                                                                                                                      | Counter 2                       | 7                                                                              |  |

|                 |                   |      | 1                                                     | 1                                                                                                                                                      | Control Word Register           |                                                                                |  |

| <u>CS</u>       | 21                | I    | CHIP SELEC                                            |                                                                                                                                                        |                                 | to respond to $\overline{RD}$ and $\overline{WR}$ signals. $\overline{RD}$ and |  |

| RD              | 22                | I    | READ: This                                            | input is low                                                                                                                                           | during CPU read operations.     |                                                                                |  |

| WR              | 23                | I    | WRITE: This input is low during CPU write operations. |                                                                                                                                                        |                                 |                                                                                |  |